K.Schneider H.Zimmermann

# Highly Sensitive Optical Receivers

# Springer Series in

# ADVANCED MICROELECTRONICS

Series Editors: K. Itoh T. Lee T. Sakurai W.M.C. Sansen D. Schmitt-Landsiedel

The Springer Series in Advanced Microelectronics provides systematic information on all the topics relevant for the design, processing, and manufacturing of microelectronic devices. The books, each prepared by leading researchers or engineers in their fields, cover the basic and advanced aspects of topics such as wafer processing, materials, device design, device technologies, circuit design, VLSI implementation, and subsystem technology. The series forms a bridge between physics and engineering and the volumes will appeal to practicing engineers as well as research scientists.

- 18 **Microcontrollers in Practice** By I. Susnea and M. Mitescu

- 19 **Gettering Defects in Semiconductors** By V.A. Perevoschikov and V.D. Skoupov

- 20 Low Power VCO Design in CMOS By M. Tiebout

- 21 Continuous-Time Sigma-Delta A/D Conversion Fundamentals, Performance Limits and Robust Implementations By M. Ortmanns and F. Gerfers

- 22 **Detection and Signal Processing**Technical Realization

By W.J. Witteman

- 23 **Highly Sensitive Optical Receivers** By K. Schneider and H.K. Zimmermann

- 24 **Bonding in Microsystem Technology** By J.A. Dziuban

# K. Schneider H. Zimmermann

# Highly Sensitive Optical Receivers

With 191 Figures and 25 Tables

# Dipl.-Ing. Dr. techn. Kerstin Schneider

Univ. Professor Dr.-Ing. Horst Zimmermann

Institute for Electrical Measurements and Circuit Design, Vienna University of Technology Gusshausstr. 25/354, A-1040 Wien, Austria

E-Mail: kerstin.schneider@tuwien.ac.at, horst.zimmermann@ieee.org

#### Series Editors:

#### Dr. Kiyoo Itoh

Hitachi Ltd., Central Research Laboratory, 1-280 Higashi-Koigakubo Kokubunji-shi, Tokyo 185-8601, Japan

#### Professor Thomas Lee

Stanford University, Department of Electrical Engineering, 420 Via Palou Mall, CIS-205 Stanford, CA 94305-4070, USA

#### Professor Takayasu Sakurai

Center for Collaborative Research, University of Tokyo, 7-22-1 Roppongi Minato-ku, Tokyo 106-8558, Japan

#### Professor Willy M. C. Sansen

Katholieke Universiteit Leuven, ESAT-MICAS, Kasteelpark Arenberg 10 3001 Leuven, Belgium

#### Professor Doris Schmitt-Landsiedel

Technische Universität München, Lehrstuhl für Technische Elektronik Theresienstrasse 90, Gebäude N3, 80290 München, Germany

ISSN 1437-0387

ISBN-10 3-540-29613-1 Springer Berlin Heidelberg New York ISBN-13 978-3-540-29613-3 Springer Berlin Heidelberg New York

Library of Congress Control Number: 2006926218

This work is subject to copyright. All rights are reserved, whether the whole or part of the material is concerned, specifically the rights of translation, reprinting, reuse of illustrations, recitation, broadcasting, reproduction on microfilm or in any other way, and storage in data banks. Duplication of this publication or parts thereof is permitted only under the provisions of the German Copyright Law of September 9, 1965, in its current version, and permission for use must always be obtained from Springer-Verlag. Violations are liable to prosecution under the German Copyright Law.

Springer is a part of Springer Science+Business Media.

springer.com

© Springer Berlin Heidelberg 2006 Printed in The Netherlands

The use of general descriptive names, registered names, trademarks, etc. in this publication does not imply, even in the absence of a specific statement, that such names are exempt from the relevant protective laws and regulations and therefore free for general use.

Camera-ready by the Author and SPi using a Springer LATEX macro package

Cover concept by eStudio Calmar Steinen using a background picture from Photo Studio "SONO".

Courtesy of Mr. Yukio Sono, 3-18-4 Uchi-Kanda, Chiyoda-ku, Tokyo

Cover design: design & production GmbH, Heidelberg

Printed on acid-free paper SPIN: 11010838 57/3100/SPI - 5 4 3 2 1 0

# Preface

The growing demand for high-speed, broadband data communication motivates the development of low-cost, high-performance optical receivers for fiber-optical networks. This book sets its focus especially on highly sensitive receivers with medium and high speed capability for the "last mile" connection in fiber-to-the-home (FTTH) systems. These connections are normally realized with infrared light with wavelengths of 1310 and 1540 nm. This fact makes it necessary for silicon optical receivers to use an external Ge or III/Vsemiconductor based photodiode. Therefore this book deals with optical receivers for detection of infrared light, including all the problems emerging from an external photodiode, such as very high input-node capacitance somewhere in the order of pF, compared to an integrated photodiode where the input-node capacitance is about an order of magnitude less, problems due to bond-wire parasitics at the input-node, etc. The influence of these problems can be clearly seen in the performance of optical receivers. The high input-node capacitance, for example, strongly influences the bandwidth and the sensitivity.

Compared to the book Integrated Silicon Optoelectronics of one of the authors, which concentrates on physics and integration of photodetectors in modern silicon bipolar, CMOS and BiCMOS processes, descriptions of fabrication technologies and properties of integrated photodetectors, and Silicon Optoelectronic Integrated Circuits, which goes deeper into the details of the circuit design of ICs with integrated photodiodes for a wide variety of applications, this book concentrates on circuit design for optical receivers with external photodiodes for optical communication. The main subject of Highly Sensitive Optical Receivers is the description of the state-of-the-art of lownoise silicon amplifiers and the comparison of bipolar, CMOS, BiCMOS, as well as SiGe amplifiers.

This new book is a summary of fundamental theory and a presentation of state-of-the-art optical receiver circuits and designs. Recent optical receivers developed by the authors show the rapid progress in optical receiver design.

The first chapter explains the motivation why all optical receivers designed by the authors are done in deep-sub-micron CMOS technology.

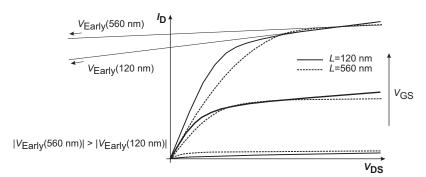

Although these deep-sub-micron CMOS technologies cause a lot of problems, due to low power supply voltage, low Early voltage and so on, this book will show that these technologies are attractive and interesting for low-noise optical receivers for medium and high data rate applications.

In particular, the newest deep-sub-micron CMOS low-noise amplifier topologies are described in detail addressing the challenging application in optical burst-mode receivers. Thereby the excellent noise properties of deep-sub-micron CMOS receivers and fast gain switching capability are highlighted. A new approach for solving the stability problem resulting from gain switching is described. This book shows how to solve the difficulties in circuit design with deep-sub-micron CMOS technologies and how to use the benefits of the technology as for example the possibility to easily integrate the analog and the digital part in systems-on-chip (SoCs). Using a standard digital deep-sub-micron CMOS process for analog design has the disadvantage of high device tolerances to deal with, but avoids costs for technology development for analog process extensions.

In the beginning of the book in Chap. 1 the motivation for burst-mode communication and the incentive to use systems-on-chip in deep-sub-micron CMOS technology are discussed.

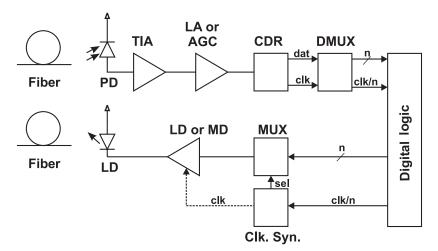

In Chap. 2 different kinds of networks are described. Furthermore continuous-mode and burst-mode access are compared. The additional requirements for burst-mode optical receivers will be discussed and the advantages of time-division-multiplex access (TDMA) will be pointed out. The increasing importance of burst-mode receivers is reflected in the growing amount of publications on this topic. In the beginning of the 1990s the first papers on burst-mode receivers were published. The number rapidly increased in the following years and is still growing. In Chap. 2, fundamental parts of optical receiver front-ends are also described. An essential part of optical receivers are the photodetectors. Photodetectors and especially SiGe photodetectors, therefore, are discussed in Chap. 3. The main focus of attention is on the preamplifier, being usually a transimpedance amplifier, in Chap. 4. Nevertheless, also main and limiting amplifiers are discussed.

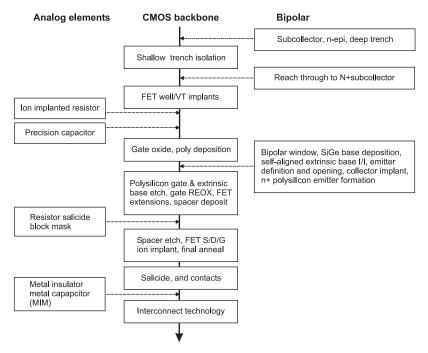

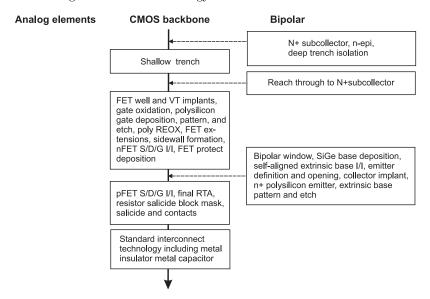

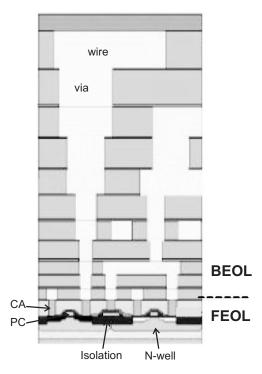

Chapter 5 gives a short overview of an SiGe heterojunction bipolar technology, as well as some more details about the deep-sub-micron CMOS processes used for the designs described in Chap. 9.

AC-analysis as well as stability analysis of several designs are contained in Chap. 6. After the feedback theory a transimpedance amplifier with an ideal amplifier is described. This is followed by an analysis of realized circuits.

Afterwards, in Chap. 7, integrated circuit technologies of current interest are described. BiCMOS, SiGe heterojunction bipolar, submicron CMOS and deep-sub-micron CMOS technologies are compared and the advantages and disadvantages of each concerning noise are described. The device properties

are compared to the properties of ideal devices and the effects of down-scaling technologies are described.

In Chap. 8 an overview of the state of the art of BiCMOS, SiGe heterojunction-bipolar and CMOS optical receivers in the literature is given. Chapter 9 summarizes the simulation environment and component models for circuit design and describes the measurement set-up and the circuits as well as printed circuit boards for characterization. Afterwards the circuits and properties of several advanced optical CMOS receivers and optical burst-mode receivers designed at the Institute for Electrical Measurements and Circuit Design at Vienna University of Technology in 0.18  $\mu m$  and 0.12  $\mu m$  standard digital CMOS are described in detail. Finally a summary of the characterized performance of the optical receivers is done. A comparison of the different designs and their results for optical receivers known from the literature follows.

The authors would like to thank their colleagues at the Institute for Electrical Measurements and Circuit Design at Vienna University of Technology for fruitful discussion and their valuable support, especially Franz Schlögl, Robert Swoboda, Michael Förtsch, Jürgen Leeb and Alexander Nemecek as well as the head of the institute, Gottfried Magerl, for his great support towards a quick start of research. Furthermore special thanks are directed to A. Wiesbauer, J. Hauptmann, M. Haas, and A. Martin from Infineon Technologies DC Villach and DC Vienna for their constant financial and technical support as well as the opportunity to use the design environment.

Vienna, June 2006

Kerstin Schneider Horst Zimmermann

Furthermore, I want to thank my parents, Bernd and Petra, for their support during my studies and especially Rainer for their patience and understanding.

Vienna, June 2006

Kerstin Schneider

# Contents

| Int           | roduction                                               | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|---------------|---------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Fur           | ndamentals                                              | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 2.1           | Point-to-Point Versus Point-to-Multipoint Access        | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|               | 2.1.1 Point-to-Point Access                             | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|               | 2.1.2 Point-to-Multipoint Access                        | 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 2.2           | Continuous-Mode Versus Burst-Mode Communication         | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|               | 2.2.1 Continuous-Mode Communication                     | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|               | 2.2.2 Burst-Mode Communication                          | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 2.3           | Components of the Optical Receiver Front-End            | 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

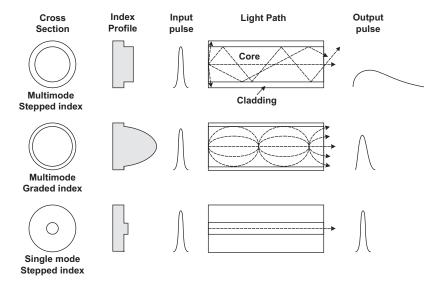

| 2.4           | Optical Fibers                                          | 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|               |                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Pho           | otodetectors                                            | 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 3.1           |                                                         | 13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 3.2           | Avalanche Photodiode                                    | 18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 3.3           | Pin Photodiode                                          | 18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 3.4           | SiGe Photodetectors                                     | 19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|               | 3.4.1 Heteroepitaxial Growth                            | 19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

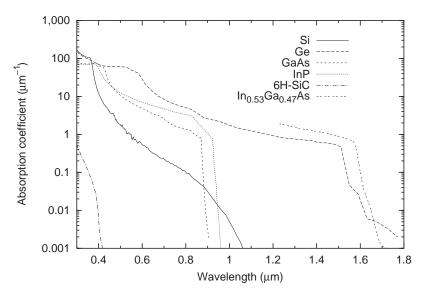

|               | 3.4.2 Absorption Coefficient of SiGe Alloys             | 21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|               | 3.4.3 Ge-on-Si IR Photodetectors                        | 21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|               | 3.4.4 SiGeC                                             | 31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

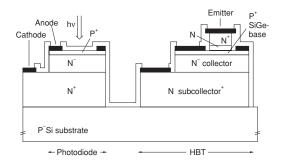

|               | 3.4.5 SiGe/Si pin Hetero Bipolar Transistor Integration | 32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| $\mathbf{Am}$ | plifiers                                                | 35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

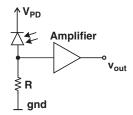

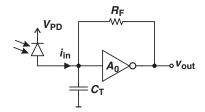

| 4.1           | Preamplifier, Transimpedance Amplifier                  | 35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 4.2           | Main Amplifier, Limiting Amplifier                      | 36                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

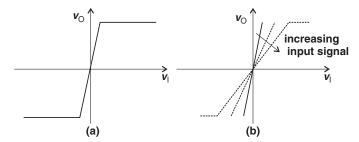

|               | 4.2.1 Limiting Amplifier                                | 37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|               | 4.2.2 AGC Amplifier                                     | 37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|               | Fur 2.1 2.2 2.3 2.4 Pho 3.1 3.2 3.3 3.4                 | 2.1.1 Point-to-Point Access 2.1.2 Point-to-Multipoint Access 2.2 Continuous-Mode Versus Burst-Mode Communication 2.2.1 Continuous-Mode Communication 2.2.2 Burst-Mode Communication 2.3 Components of the Optical Receiver Front-End 2.4 Optical Fibers  Photodetectors 3.1 Basics of Photodetectors 3.2 Avalanche Photodiode 3.3 Pin Photodiode 3.4 SiGe Photodetectors 3.4.1 Heteroepitaxial Growth 3.4.2 Absorption Coefficient of SiGe Alloys 3.4.3 Ge-on-Si IR Photodetectors 3.4.4 SiGeC 3.4.5 SiGe/Si pin Hetero Bipolar Transistor Integration  Amplifiers 4.1 Preamplifier, Transimpedance Amplifier 4.2 Main Amplifier, Limiting Amplifier 4.2.1 Limiting Amplifier |

| X | Contents |

|---|----------|

|   |          |

| 5 | Inte  | grated Circuit Technology                                        |     |

|---|-------|------------------------------------------------------------------|-----|

|   | 5.2   | Deep-Sub-Micron CMOS                                             |     |

| 6 | Trai  | nsimpedance Amplifier Theory                                     | 51  |

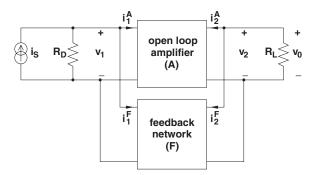

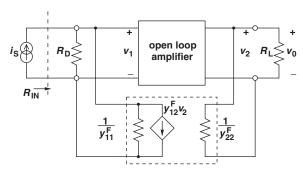

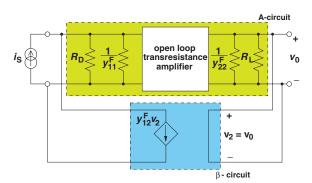

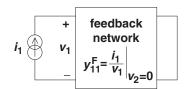

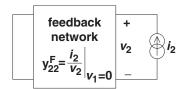

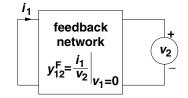

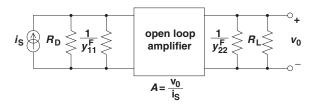

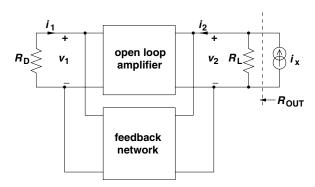

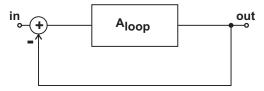

|   | 6.1   | Feedback Theory                                                  | 51  |

|   |       | 6.1.1 Shunt–Shunt Feedback                                       | 51  |

|   |       | 6.1.2 Input and Output Resistance                                | 55  |

|   | 6.2   | TIA with Ideal Amplifier                                         | 57  |

|   | 6.3   | TIA with Frequency-Dependent Open-Loop Gain                      | 58  |

|   |       | 6.3.1 TIA with Folded-Cascode Amplifier Stage                    | 59  |

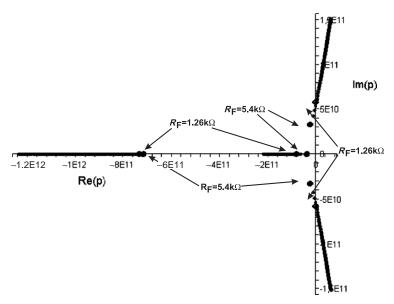

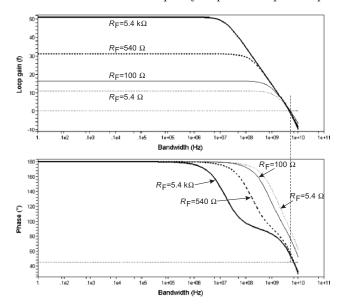

|   |       | 6.3.2 TIA with Inverter Amplifier Stages                         | 63  |

|   |       | 6.3.3 Transimpedance-Gain Switching and Stability of TIA         |     |

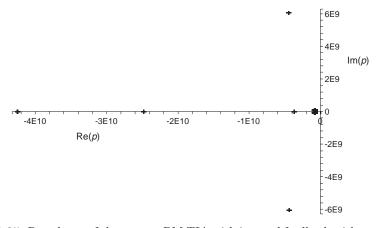

|   |       | with Inverter Amplifier Stages                                   | 70  |

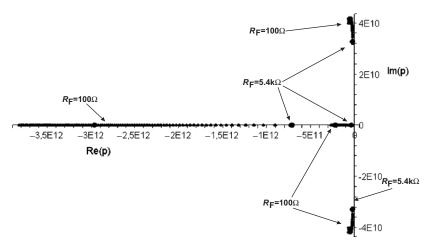

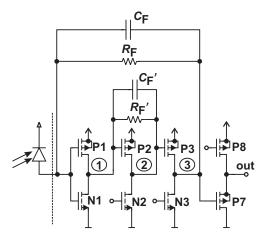

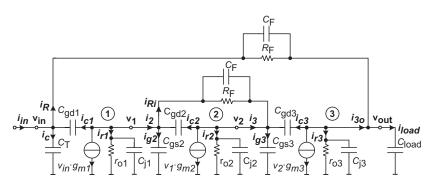

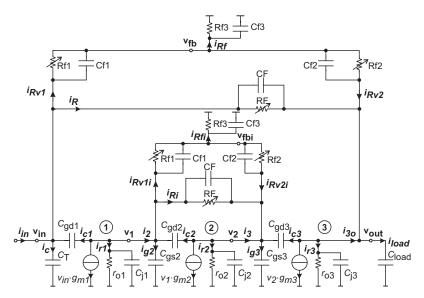

|   |       | 6.3.4 Three-Stage Burst-Mode TIA with Internal Feedback          | 76  |

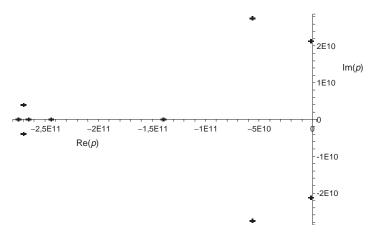

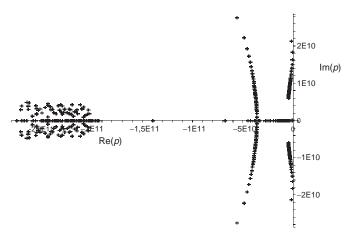

|   |       | 6.3.5 Transimpedance-Gain Switching and Stability of             |     |

|   |       | Three-Stage Burst-Mode TIA with Internal Feedback                | 79  |

| 7 | Nois  | se Theory                                                        | 85  |

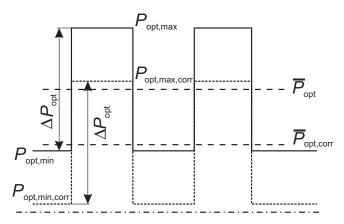

|   | 7.1   | Sensitivity and Power Penalty                                    | 85  |

|   |       | 7.1.1 Bit-Error Rate                                             | 85  |

|   |       | 7.1.2 Sensitivity                                                | 89  |

|   |       | 7.1.3 Power Penalty                                              | 89  |

|   | 7.2   | Noise Models of Components                                       | 91  |

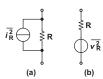

|   |       | 7.2.1 Resistor Noise Model                                       | 92  |

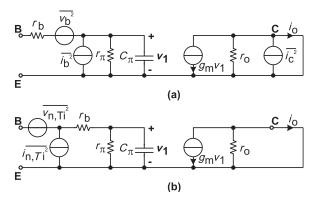

|   |       | 7.2.2 Bipolar- and Heterojunction-Bipolar-Transistor Noise Model | 93  |

|   |       | 7.2.3 Field-Effect-Transistor Noise Model                        | 96  |

|   | 7.3   | Noise Models of Transimpedance Amplifier                         | 99  |

|   | • • • | 7.3.1 Ideal-Amplifier TIA                                        | 99  |

|   |       | 7.3.2 TIA with Bipolar and Heterojunction Bipolar Input          |     |

|   |       | Stage                                                            | 100 |

|   |       | 7.3.3 TIA with MOS Input Stage                                   |     |

|   |       | 7.3.4 Comparison of Bipolar and Field-Effect Transistor          |     |

|   |       | Circuits Based on Noise Theory                                   | 101 |

|   | 7.4   | Noise Models of More Complex TIAs in Deep-Sub-micron             |     |

|   |       | CMOS Technology                                                  | 104 |

|   |       | 7.4.1 Noise Analysis of Folded-Cascode TIA                       |     |

|   |       | 7.4.2 TIA with CMOS-Inverter Input Circuit                       |     |

| 8 | Stat  | se of the Art                                                    | 115 |

|   | 8.1   | Silicon Bipolar and BiCMOS Optical Receivers                     |     |

|   | 8.2   | SiGe Heterojunction Bipolar and SiGe BiCMOS Optical              |     |

|   |       | Receivers                                                        | 121 |

|   | 8.3   | Silicon CMOS Optical Receivers                                   |     |

|      |            |       | Contents                                              | XI  |

|------|------------|-------|-------------------------------------------------------|-----|

| 8    | 8.4        | Summ  | nary of Results of State-of-the-Art Optical Receivers | 135 |

| 9    | Dee        | p-Sub | -μm CMOS Circuits                                     | 139 |

|      | 9.1        |       | ation Environment and Component Models                |     |

|      |            | 9.1.1 | Simulation Environment                                | 139 |

|      |            | 9.1.2 | Photodiode Model                                      | 139 |

|      |            | 9.1.3 | MOSFET Model                                          | 141 |

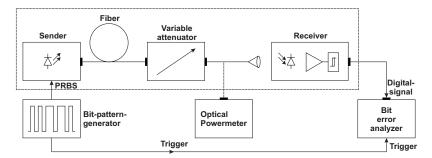

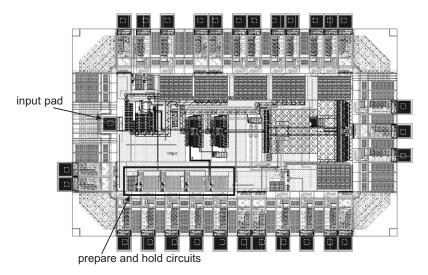

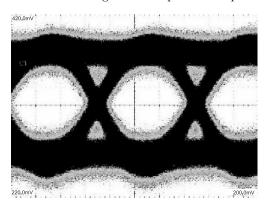

| 9    | 9.2        | Chara | acterization Setup                                    | 145 |

|      | 9.3        |       | ns and Properties of Optical Receivers                |     |

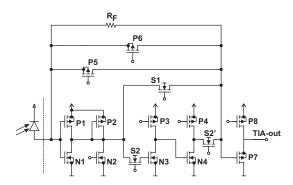

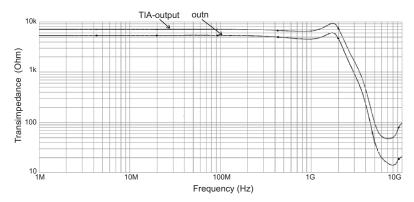

|      |            | 9.3.1 | Folded-Cascode Transimpedance Amplifier               |     |

|      |            | 9.3.2 | Three-Inverter Transimpedance Amplifier               |     |

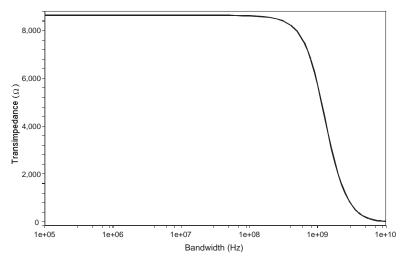

|      |            | 9.3.3 | Three-Stage Transimpedance Amplifier                  | 154 |

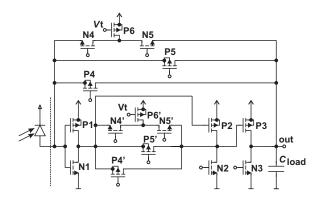

|      |            | 9.3.4 | Three-Stage Burst-Mode Transimpedance Amplifier       |     |

|      |            |       | with Internal Feedback                                | 159 |

|      |            | 9.3.5 | Three-Stage Burst-Mode Transimpedance Amplifier       |     |

|      |            |       | for $2.5\mathrm{Gb}\mathrm{s}^{-1}$                   | 163 |

|      |            | 9.3.6 | Three-Stage Burst-Mode Transimpedance Amplifier       |     |

|      |            |       | for Ultra-Fast Gain Switching                         | 169 |

| 9    | 9.4        | Summ  | nary and Comparison                                   |     |

| Refe | ren        | ces   |                                                       | 183 |

| Inde | · <b>X</b> |       |                                                       | 193 |

# List of Symbols

| Symbol                             | Description                                          | Units                  |

|------------------------------------|------------------------------------------------------|------------------------|

| A                                  | Area                                                 | $\mathrm{mm}^2$        |

| $A_0$                              | Low-frequency open-loop gain                         |                        |

| A(f)                               | Frequency-dependent gain                             |                        |

| $A_{\text{loop}}$                  | Loop gain                                            |                        |

| $A_{3I}(f)$                        | Frequency-dependent gain of three-inverter amplifier |                        |

| $A_{\mathrm{FC}}(f)$               | Frequency-dependent gain of folded-cascode circuit   |                        |

| $A_{ m TIA}$                       | Effective transimpedance of TIA                      | $\Omega$               |

| c                                  | Speed of light in a medium                           | ${ m cms^{-1}}$        |

| $c_0$                              | Speed of light in vacuum                             | ${\rm cms^{-1}}$       |

| $C_{ m F}$                         | Feedback capacitance                                 | F                      |

| $C_{ m gd}$                        | Gate-drain capacitance                               | F                      |

| $C_{ m gd} \ C_{ m gs} \ C_{ m j}$ | Gate-source capacitance                              | F                      |

| $C_{ m j}$                         | Junction capacitance                                 | F                      |

| $C_{ m ox}$                        | Gate oxide capacitance per unit area                 | ${ m fF}/{ m \mu m}^2$ |

| $C_{ m pd}$                        | Photodiode capacitance                               | $\mathbf{F}$           |

| $C_{ m para}$                      | Parasitic capacitance                                | F                      |

| $C_{ m T}$                         | Input-node capacitance                               | F                      |

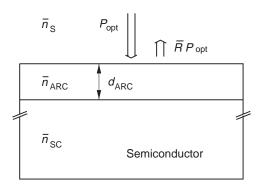

| $d_{ m ARC}$                       | Thickness of antireflecting coating                  | $\mu \mathrm{m}$       |

| $d_{ m I}$                         | Thickness of intrinsic region                        | $\mu \mathrm{m}$       |

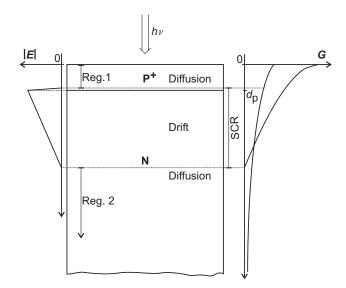

| $d_{ m p}$                         | Thickness of p-type region                           | $\mu \mathrm{m}$       |

| $\overline{F}$                     | Lowering factor for stability analysis               |                        |

| f                                  | Frequency                                            | Hz                     |

| $f_{-3\mathrm{dB}}$                | $-3 \mathrm{dB}$ cut-off frequency                   | Hz                     |

| $f_{eta}$                          | $-3\mathrm{dB}$ cut-off frequency of $\beta$         | Hz                     |

| $f_g$                              | $-3\mathrm{dB}$ frequency bandwidth                  | Hz                     |

| Symbol                                                                                                                                                                                                                                                                                                   | Description                                          | Units                          |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|--------------------------------|

| $g_{ m ds}$                                                                                                                                                                                                                                                                                              | Transistor output conductance                        | $\mathrm{A}\mathrm{V}^{-1}$    |

| $g_{ m m}$                                                                                                                                                                                                                                                                                               | Transconductance                                     | ${ m AV^{-1}}$                 |

| $g_{ m m}^{ m I}$                                                                                                                                                                                                                                                                                        | Transconductance of inverter                         | ${ m AV^{-1}}$                 |

| h                                                                                                                                                                                                                                                                                                        | Plack constant                                       | $_{ m Js}$                     |

| $\hbar$                                                                                                                                                                                                                                                                                                  | $h/2\pi$                                             | $_{ m Js}$                     |

| $\langle i_0 \rangle$                                                                                                                                                                                                                                                                                    | Mean photocurrent for logical zero                   | A                              |

| $\langle i_1 \rangle$                                                                                                                                                                                                                                                                                    | Mean photocurrent for logical one                    | A                              |

| $\begin{array}{l} \langle i_1 \rangle \\ i_{\rm L} \\ i^{\overline{2}} \\ \overline{i_{\rm o}^2} \\ \overline{i_{\rm o}^2} \\ \overline{i_{\rm b}^2} \\ \overline{i_{\rm d}^2} \\ \overline{i_{\rm d}^2} \\ \overline{i_{\rm g}^2} \\ \overline{i_{\rm c}^2} \\ i_{\rm c} \\ x \\ i_{\rm o} \end{array}$ | Leakage current of photodiode                        | A                              |

| $\overline{i^2}$                                                                                                                                                                                                                                                                                         | Spectral noise current density                       | $A^2$                          |

| $\overline{i_0^2}$                                                                                                                                                                                                                                                                                       | Spectral noise output noise current density          | $\mathrm{A}^2\mathrm{Hz}^{-1}$ |

| $\overline{i_{\rm h}^2}$                                                                                                                                                                                                                                                                                 | Base current noise source                            | $A^2$                          |

| $\frac{\overline{b}}{i^2}$                                                                                                                                                                                                                                                                               | Collector current noise source                       | $\mathrm{A}^2$                 |

| $\frac{c}{i^2}$                                                                                                                                                                                                                                                                                          | Drain current noise source                           | $A^2$                          |

| $\frac{d}{i^2}$                                                                                                                                                                                                                                                                                          | Gate current noise source                            | $A^2$                          |

| $i_{\mathrm{g}}$                                                                                                                                                                                                                                                                                         | Small-signal capacitance current of stage $x$        | A                              |

| $i_{\mathcal{C}} x$                                                                                                                                                                                                                                                                                      | Small-signal output current                          | A                              |

| $i_{-}$                                                                                                                                                                                                                                                                                                  | Small-signal resistance current of stage $x$         | A                              |

| <u>i2</u>                                                                                                                                                                                                                                                                                                | Spectral resistor noise current density              | $ m A^2Hz^-$                   |

| $\frac{i_{\text{rx}}}{i_{\text{n,R}}^2}$ $\frac{i_{\text{n,R}}^2}{i_{\text{n,in}}^2}$ $\frac{i_{\text{n,in}}^2}{i_{\text{n,amp}}^2}$                                                                                                                                                                     |                                                      |                                |

| $\frac{i_{n,in}^2}{i_{n,in}^2}$                                                                                                                                                                                                                                                                          | Equivalent input noise current density               | $A^2 Hz^{-1}$                  |

| $\frac{i_{n,amp}^2}{2}$                                                                                                                                                                                                                                                                                  | Equivalent input noise current density of amplifier  | $A^2 Hz^{-1}$                  |

| $i_{ m n,Ti}^2$                                                                                                                                                                                                                                                                                          | Equivalent input noise current density of transistor | ${ m A^2Hz^{-1}}$              |

| I                                                                                                                                                                                                                                                                                                        | Current                                              | A                              |

| $I_{ m in}$                                                                                                                                                                                                                                                                                              | Input current                                        | A                              |

| $I_{ m ph}$                                                                                                                                                                                                                                                                                              | Photocurrent                                         | A                              |

| $I_{ m B}$                                                                                                                                                                                                                                                                                               | Base current                                         | A                              |

| $I_{ m C}$                                                                                                                                                                                                                                                                                               | Collector current                                    | A                              |

| $I_{ m D}$                                                                                                                                                                                                                                                                                               | Drain current                                        | A                              |

| $I_{ m E}$                                                                                                                                                                                                                                                                                               | Emitter current                                      | A                              |

| $I_{ m S}$                                                                                                                                                                                                                                                                                               | Source current                                       | A                              |

| $k_{\mathrm{B}}$                                                                                                                                                                                                                                                                                         | Boltzmann constant                                   | $ m JK^{-1}$                   |

| $k_{\rm B}T$                                                                                                                                                                                                                                                                                             | Thermal energy                                       | $\mathrm{eV}$                  |

| L                                                                                                                                                                                                                                                                                                        | Length                                               | μm                             |

| $L_{ m B}$                                                                                                                                                                                                                                                                                               | Inductance of bond wire                              | Η                              |

| $L_{ m D}$                                                                                                                                                                                                                                                                                               | Diffusion length                                     | nm                             |

| $\overline{n}$                                                                                                                                                                                                                                                                                           | Refractive index                                     |                                |

| $\overline{n_1}$                                                                                                                                                                                                                                                                                         | Refractive index of fiber core                       |                                |

| $\overline{n_2}$                                                                                                                                                                                                                                                                                         | Refractive index of fiber cladding                   |                                |

| $\frac{\overline{n_{\mathrm{ARC}}}}{\underline{-}}$                                                                                                                                                                                                                                                      | Refractive index of antireflecting coating           |                                |

| $\overline{n_{\mathrm{s}}}$                                                                                                                                                                                                                                                                              | Refractive index of surroundings                     |                                |

| $\overline{n_{ m sc}}$                                                                                                                                                                                                                                                                                   | Refractive index of semiconductor                    |                                |

| Symbol                                                                                                                                                                                           | Description                                          | Units                   |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|-------------------------|

| $P_{\rm char}$                                                                                                                                                                                   | Characteristic polynomial                            |                         |

| $P_{ m opt}$                                                                                                                                                                                     | Incident optical power                               | W                       |

| $p_0(i)$                                                                                                                                                                                         | Probability density for a logical zero               |                         |

| $p_1(i)$                                                                                                                                                                                         | Probability density for a logical one                |                         |

| $\overline{P_{ m opt}}$                                                                                                                                                                          | Average incident optical power                       | W                       |

| *                                                                                                                                                                                                | Magnitude of electronic charge                       | As                      |

| $rac{q}{R}$                                                                                                                                                                                     | Reflectivity                                         |                         |

| $r_{ m b}$                                                                                                                                                                                       | Base series resistance                               | $\Omega$                |

| $r_{ m c}$                                                                                                                                                                                       | Small-signal collector series resistance             | $\Omega$                |

| $r_{ m o}$                                                                                                                                                                                       | Small-signal output resistance                       | $\Omega$                |

| $r_{ m d}$                                                                                                                                                                                       | Small-signal drain series resistance                 | $\Omega$                |

| $r_{ m s}$                                                                                                                                                                                       | Small-signal source series resistance                | $\Omega$                |

| $r_{ m DS}$                                                                                                                                                                                      | Small-signal output resistance                       | $\Omega$                |

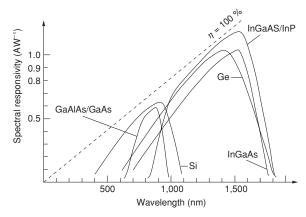

| R                                                                                                                                                                                                | Responsivity                                         | ${ m AW^{-1}}$          |

| $R_{ m F}$                                                                                                                                                                                       | Feedback resistance                                  | $\Omega$                |

| $R_{ m S}$                                                                                                                                                                                       | Series resistance                                    | $\Omega$                |

| $R_{ m L}$                                                                                                                                                                                       | Load resistance                                      | $\Omega$                |

| S                                                                                                                                                                                                | Spacing                                              | $\mu\mathrm{m}$         |

| <u>;</u>                                                                                                                                                                                         | Time                                                 | S                       |

| $t_{ m f}$                                                                                                                                                                                       | Fall time                                            | S                       |

| r                                                                                                                                                                                                | Rise time                                            | S                       |

| $\Gamma$                                                                                                                                                                                         | Absolute temperature                                 | K                       |

| $\Gamma_{\rm p}$                                                                                                                                                                                 | Period interval                                      | S                       |

| $\frac{1}{\sqrt{2}}$                                                                                                                                                                             | Base resistor noise voltage                          | $V^2$                   |

| $\frac{D}{D}$                                                                                                                                                                                    | Spectral resistor noise voltage density              | $ m V^2Hz^{-1}$         |

| $\frac{\kappa}{v^2}$                                                                                                                                                                             | Equivalent input noise voltage density of amplifier  | $ m V^2Hz^{-1}$         |

| $T_{\text{p}}$ $\frac{T_{\text{p}}}{\sqrt{2}}$ $\frac{V_{\text{b}}^2}{\sqrt{2}}$ $\frac{V_{\text{n,amp}}^2}{\sqrt{2}}$ $\frac{V_{\text{n,in}}^2}{\sqrt{2}}$ $\frac{V_{\text{n,Ti}}^2}{\sqrt{2}}$ | Equivalent input noise voltage density               | $V^2  \mathrm{Hz}^{-1}$ |

| ,2                                                                                                                                                                                               | Equivalent input noise voltage density of transistor | $ m V^2Hz^{-1}$         |

| $V^{\mathrm{n,Ti}}$                                                                                                                                                                              | Voltage                                              | V                       |

| $V_{ m BE}$                                                                                                                                                                                      | Base–emitter voltage                                 | V                       |

| $V_{ m br}$                                                                                                                                                                                      | Breakdown voltage                                    | V                       |

| $V_{ m DS}$                                                                                                                                                                                      | Drain-source voltage                                 | V                       |

| $V_{ m Early}$                                                                                                                                                                                   | Early voltage                                        | V                       |

| $V_{ m GS}$                                                                                                                                                                                      | Gate—source voltage                                  | V                       |

| $V_{ m pin}$                                                                                                                                                                                     | Photodiode voltage                                   | V                       |

| $V_{ m T}$                                                                                                                                                                                       | Thermal voltage $k_{\rm B}{\rm Tq^{-1}}$             | V                       |

| $V_{ m Th}$                                                                                                                                                                                      | Threshold voltage                                    | V                       |

| $V_{ m o}$                                                                                                                                                                                       | Output voltage                                       | V                       |

| W                                                                                                                                                                                                | Width                                                | μm                      |

| $Z_{ m F}$                                                                                                                                                                                       | Feedback impedance of transimpedance amplifier       | $\Omega$                |

XVI List of Symbols

| Symbol                        | Description                                         | Units                 |

|-------------------------------|-----------------------------------------------------|-----------------------|

| $\alpha$                      | Absorption coefficient                              | $\mu \mathrm{m}^{-1}$ |

| $\beta$                       | Current gain of bipolar transistor                  |                       |

| $\epsilon_0$                  | Permittivity in vacuum                              | ${ m Fcm^{-1}}$       |

| $\epsilon_{ m r}$             | Relative permittivity                               |                       |

| $\epsilon_{ m s}$             | Semiconductor permittivity                          | ${ m Fcm^{-1}}$       |

| $\eta$                        | Quantum efficiency                                  | %                     |

| $\eta_{ m e}$                 | External (total) quantum efficiency                 | %                     |

| $\eta_{ m i}$                 | Internal quantum efficiency                         | %                     |

| $\frac{\dot{\kappa}}{\kappa}$ | Extinction coefficient                              |                       |

| $\lambda$                     | Wavelength in a medium                              | nm                    |

| $\lambda_0$                   | Wavelength in vacuum                                | nm                    |

| $\omega$                      | Angular frequency                                   | $s^{-1}$              |

| $\omega_{ m g}$               | $2\pi f_{ m g}$                                     | $s^{-1}$              |

| $arGamma_{ m F}$              | Gamma factor (2/3 for Si FETs in saturation region) |                       |

# Introduction

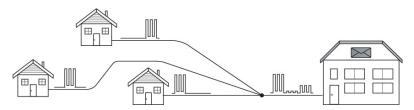

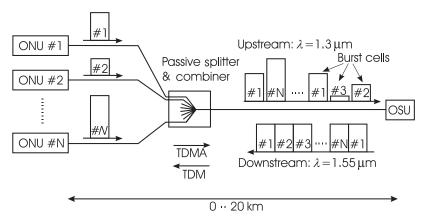

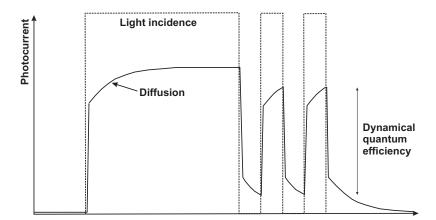

For long-haul and ultra-high-speed data communication, fiber-optical networks with optical amplifiers have become the main technology and do not require receivers with highest sensitivity [1,2]. The growing demand on broadband Internet access, however, has motivated development of low-cost, high-sensitivity optical receivers with a wide dynamic range for the optical input power. The gap of transmission bandwidth at the "last mile" can be closed by fibers-to-the-home (FTTH) at medium data rates. Figure 1.1 shows the principle of a passive optical network. The three homes in the example are connected to the post office on the right-hand side via a passive optical star coupler. The homes are sending in time-division multiplex access (TDMA) in a well-defined order. Due to the different distances between the homes and the receiver in the post office the attenuation is different and therefore the received signals are in a wide optical power range. A burst-mode receiver is necessary to handle the incoming signals.

Bipolar, CMOS, BiCMOS, and SiGe receivers are compared in this book. Therefore also the technologies are compared concerning noise, and receivers in these technologies are presented and compared. Bipolar transistors are faster than CMOS transistors with the same structure size and have the advantage of higher transconductance. The matching of bipolar transistors is also better than that of MOSFETs.

CMOS technologies have the advantage that they are faster on the market than bipolar or BiCMOS technologies. Especially BiCMOS technologies with the same minimum structure as CMOS technologies are normally available a few years later and are more expensive than CMOS processes of the same structure size. However, analog circuits in a 120 nm CMOS process can be realized with a similar or equal performance as in a sub-micron bipolar or BiCMOS process (e.g., 0.6 or 0.35  $\mu m$ ). If systems-on-chip including large digital parts with a large number of transistors are needed, deep-sub-micron CMOS, however, is an advantage compared to sub-micron BiCMOS technologies, because the chip area for the digital part is much less in deep-sub-micron

Fig. 1.1. Example configuration for a passive optical network

CMOS. It has to be mentioned, however, that for low volumes of ICs or ASICs deep-sub-micron CMOS circuits are much more expensive than sub-micron BiCMOS chips due to the large difference of mask costs.

Due to increasing doping levels of wells, channels, and substrate in down-scaling technologies, the width of the space-charge region is reduced. Also the electric field strength increases and therefore low supply voltages are necessary to stay below the breakdown field strength. These low supply voltages are the reason why classical methods of circuit design, e.g., the classical cascode circuit are no longer useable.

The low-noise optical receivers presented in this book are designed in standard digital 180 nm CMOS as well as 120 nm CMOS technology to show the low-noise capability of deep-sub-micron CMOS for high photodiode capacitance. The reason for choosing deep-sub-micron CMOS technology was the possibility to easily integrate a signal-processing digital part. The signal does not leave the chip after the optical receiver and therefore output drivers and output impedance matching can be saved in systems-on-a-chip (SoCs). Packaging costs and influences of parasitic elements, e.g., from electrostatic discharge (ESD)-structures, bond-pads and bond wires are avoided in SoCs.

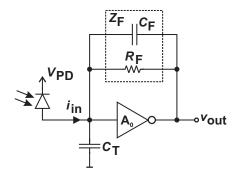

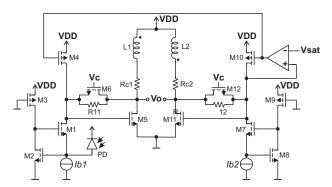

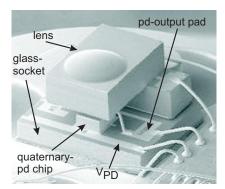

To detect the infrared light of  $\lambda=1.3\,\mu\mathrm{m}$ , an external quaternary photodiode is necessary. This external photodiode causes a high input-node capacitance. The transimpedance amplifiers (TIA) in deep-sub-micron CMOS presented in this work, nevertheless, show a high sensitivity and a wide input-current range. To avoid overdrive, the transimpedance has to be variable. Therefore, usually switching of the compensation capacitance is necessary to guarantee stability. The parasitic capacitances of the MOSFET switches, however, reduce the data rate and sensitivity in these designs. Another solution for this problem is suggested here. Reducing the open-loop gain of the amplifier in order to achieve stability instead of switching the feedback capacitance enables a high dynamic optical input power range and high data rates.

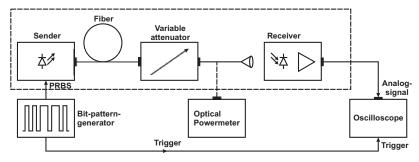

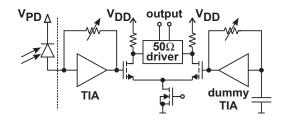

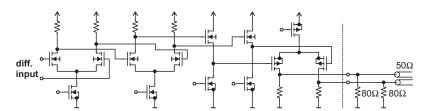

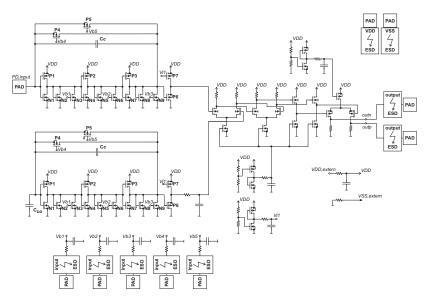

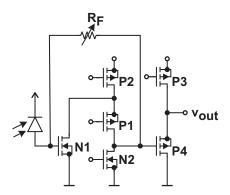

The focus of this work is on the development of the preamplifier of the optical deep-sub-micron CMOS receiver. This is normally a TIA and due to the fact that there is no digital part integrated in the test-chips introduced here the biasing voltages are generated externally. Furthermore, a  $50\,\Omega$  driver is implemented to drive the measurement system. In the final design the optical receiver front-end is followed by a main amplifier and the digital part and therefore the circuit for characterization is not necessary in the final system.

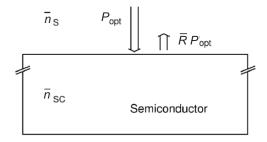

Fundamentals of network access and the difference between continuous-mode and burst-mode communication are discussed in Chap. 2. Furthermore the components of the optical receiver front-end are summarized. Photodetectors are described in Sect. 3. An overview of the basic knowledge about transimpedance and main and limiting amplifiers is given in Sect. 4.

In Chap. 5 a short overview of the used deep-sub-micron CMOS processes is presented. The disadvantages and the challenge of using a standard digital technology for an analog design is pointed out.

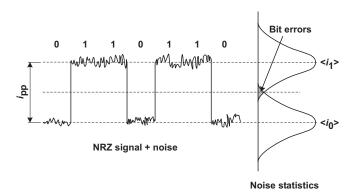

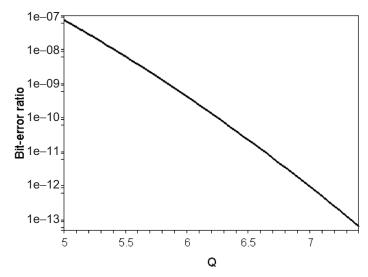

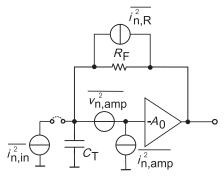

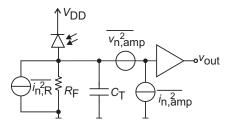

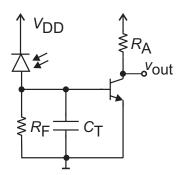

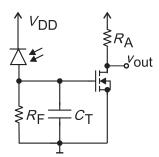

Chapter 6 processes the circuit theory of the transimpedance amplifier (TIA) with a section about stability. Chapter 7 introduces bit-error rate and sensitivity and in the following the noise theory of transistors on the one hand and TIAs on the other. First the circuit of an ideal TIA is analyzed and after this a real TIA is examined more closely. The noise theory first describes the main parameters having influence on the sensitivity, the bit-error ratio, the power penalty and the noise of the input circuit. The noise model of field-effect transistors is summarized and the noise of the input circuit is calculated for a TIA with an ideal, but noisy amplifier and for TIAs with two different CMOS input stages realized during this work.

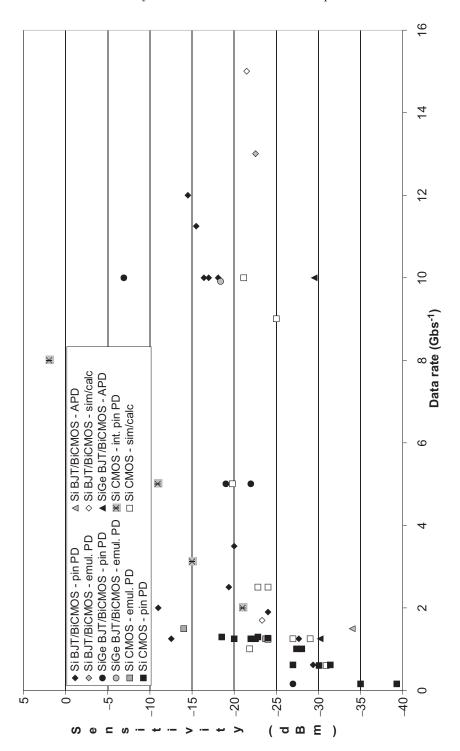

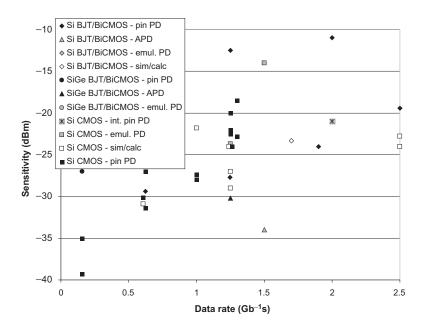

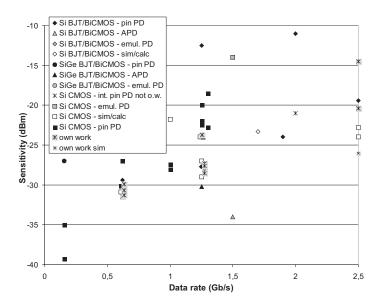

Before our own designs are presented, an overview of the state of the art in bipolar, CMOS, BiCMOS, and SiGe optical receivers is given in Chap. 8. It includes highly sensitive optical continuous-mode receivers as well as real burst-mode receivers.

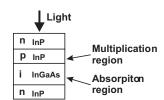

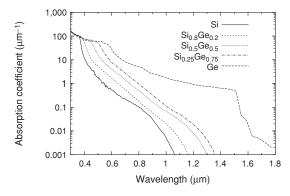

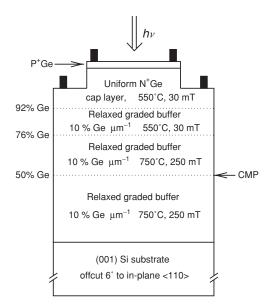

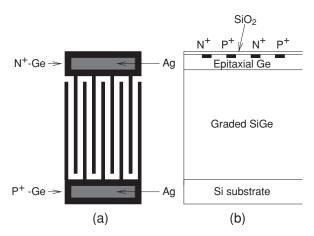

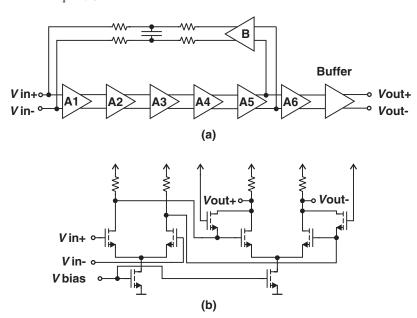

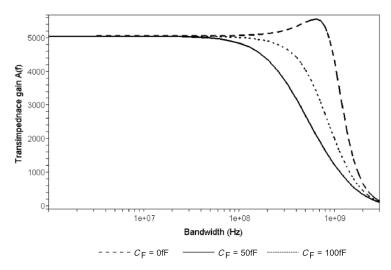

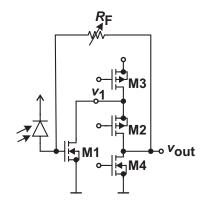

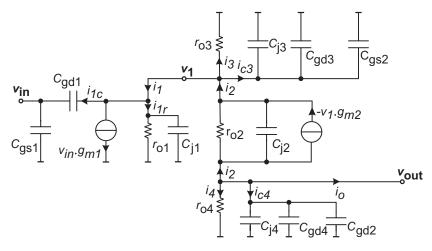

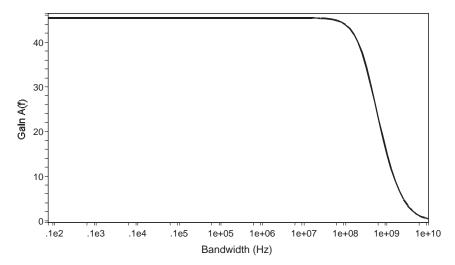

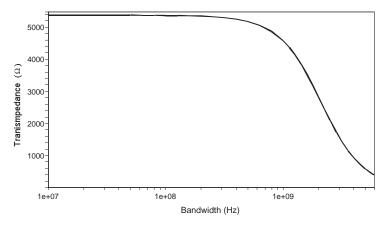

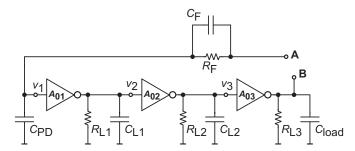

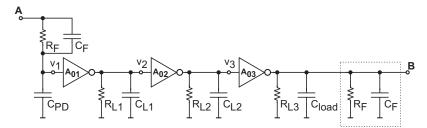

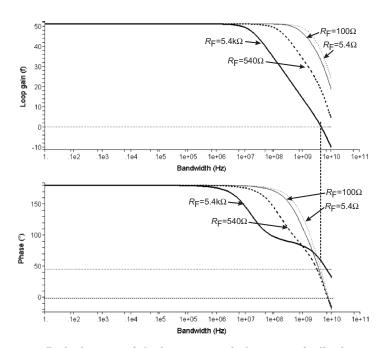

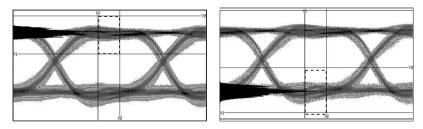

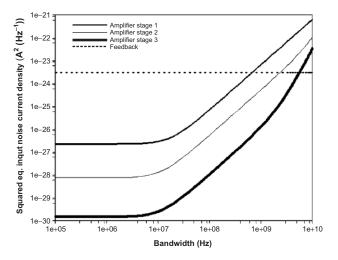

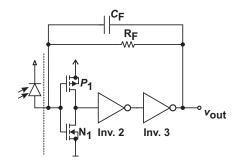

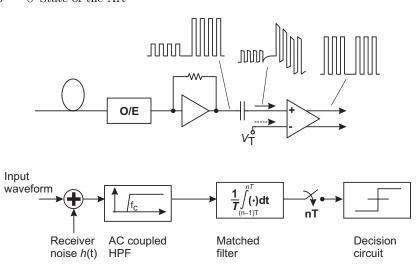

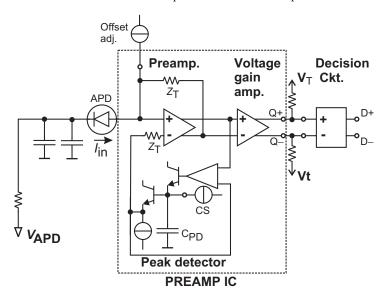

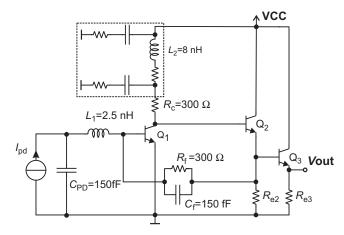

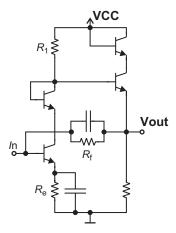

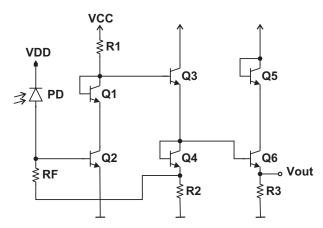

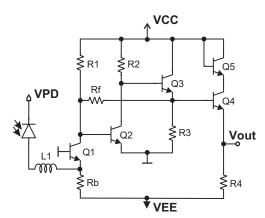

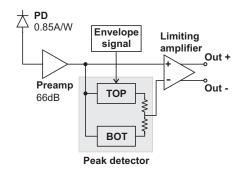

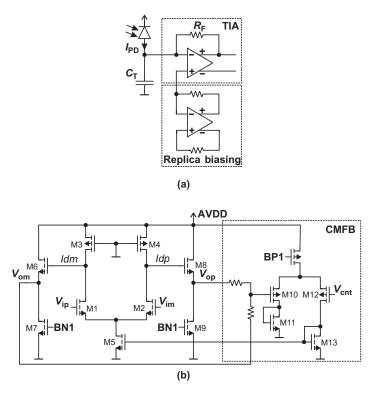

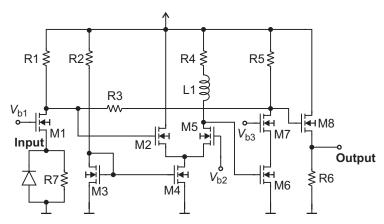

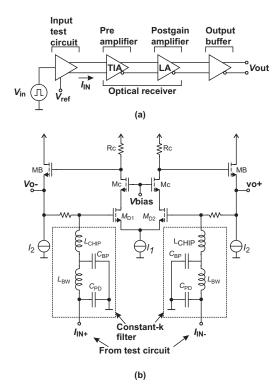

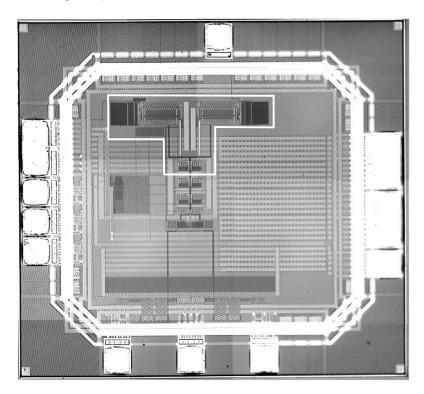

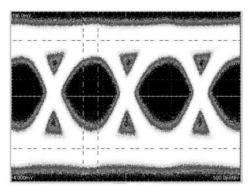

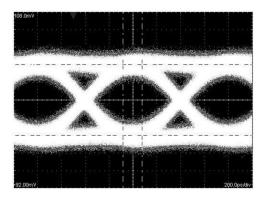

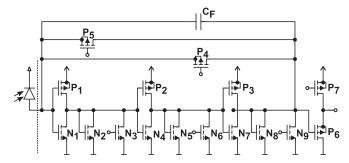

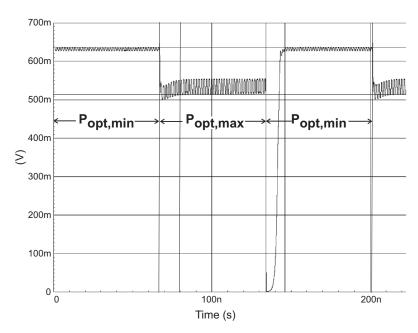

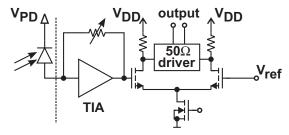

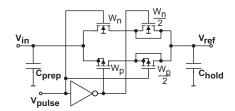

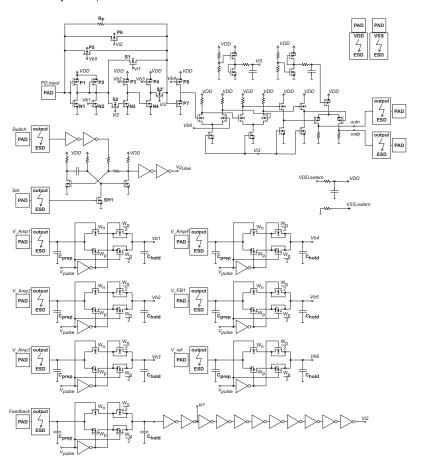

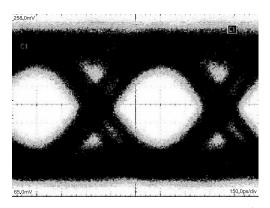

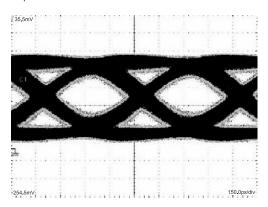

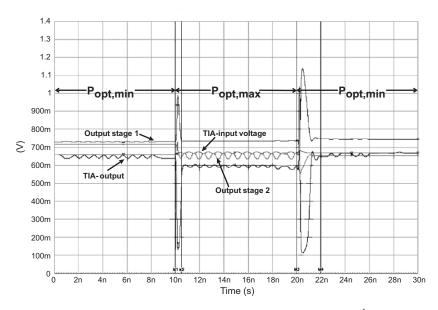

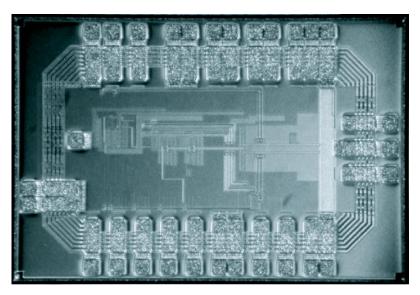

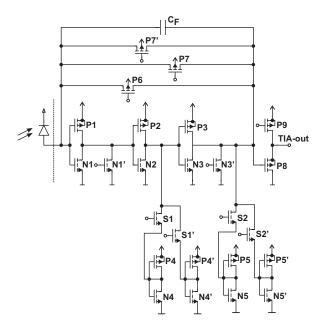

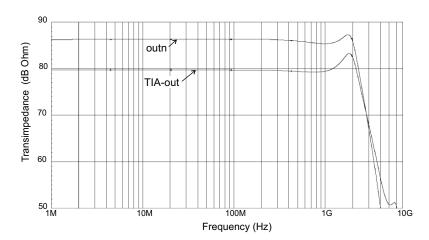

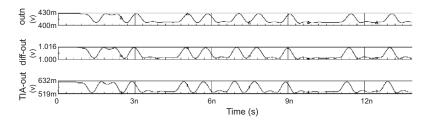

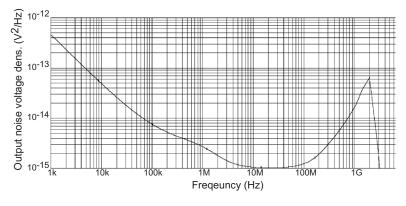

The developed designs are presented in the last chapter. First, the design environment and the measurement setup are discussed and the schematics as well as layout plots and measured results are presented. At the end of the chapter a conclusion and a comparison of our own designs with the state of the art is given.